# 管内エンジニア向け FPGAリテラシー向上研修

- ✓ アプリ・生産技術・メカ・エレキ・全てのエンジニアを対象とした、FPGAの性能をフルで引き出すためのスキルアップ研修！

- ✓ 生産性向上・省人化・省エネ化のため全てのエンジニアはFPGAの性能をフルに引き出せるようになる必要アリ！

情報政策・半導体戦略室

2025/12/4

# 管内エンジニア向けのFPGA研修/リスクリングの場を設定

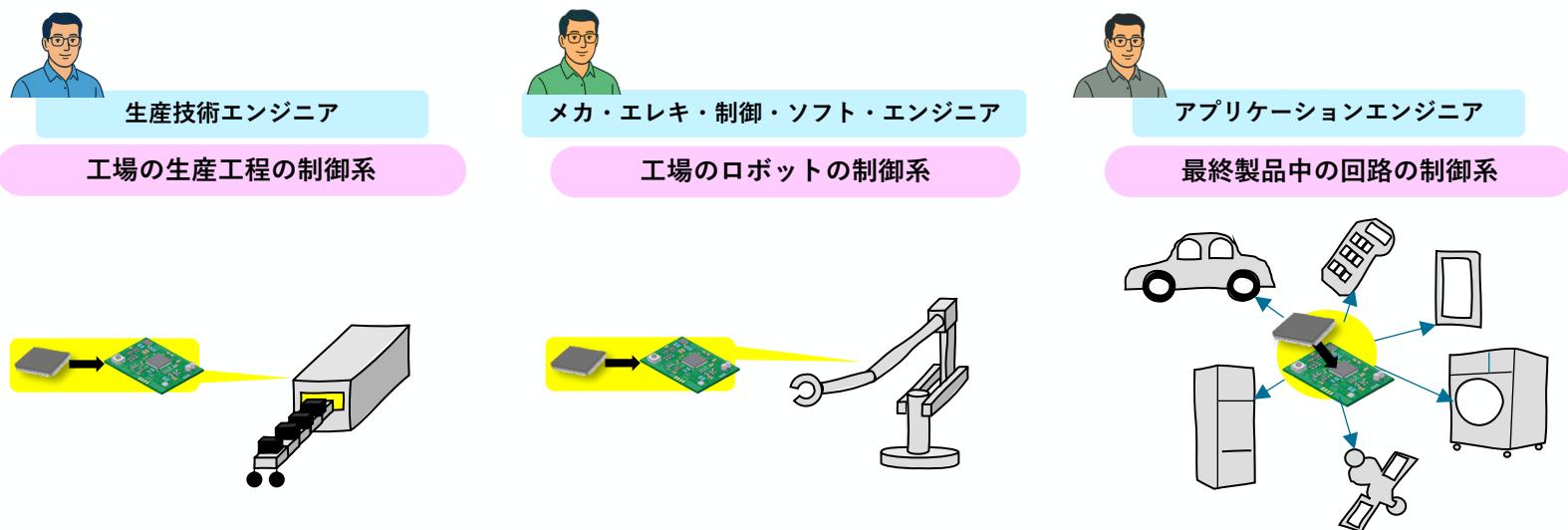

- 生産技術・メカ・エレキ・制御・ソフト・アプリなどのエンジニアは少なからずFPGA等に「触れる」機会がある。

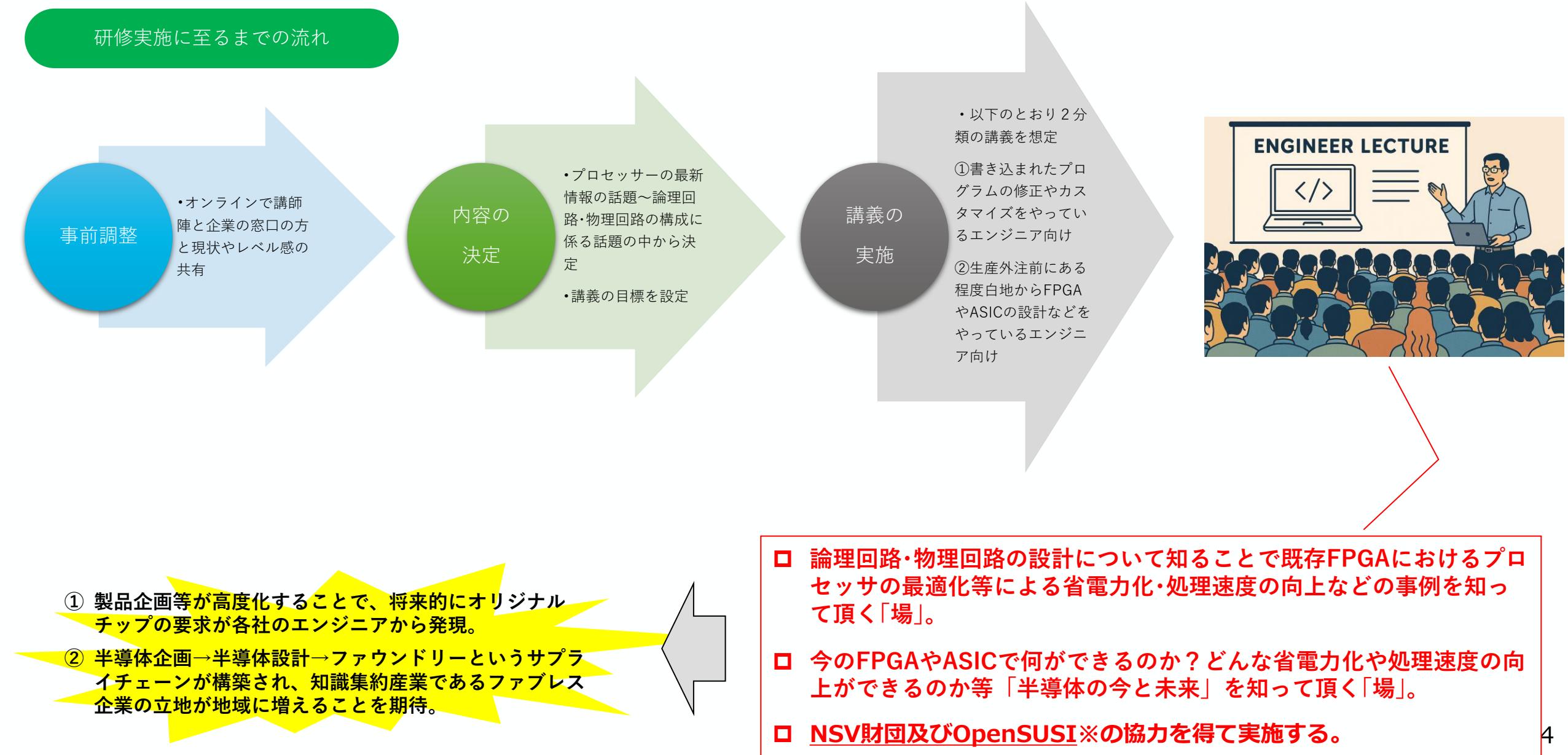

- 今回、FPGA等を「触っている」エンジニア向けに大きく2分野に分けた研修/リスクリングの場を試行的に提供します。

- レベル感・人物像は次のとおり。

## 人物像①

書き込まれたプログラムの修正やカスタマイズをやっているエンジニア

■FPGAの論理設計や物理設計についての講義

<効果の例>

→最適なプログラム修正が可能となり、設備の処理速度が向上する。

## 人物像②

生産外注前にある程度白地からFPGAやASICの設計などをやっているエンジニア

# 問題意識：最新情報の欠如がエンジニアリング上の制約条件になっている

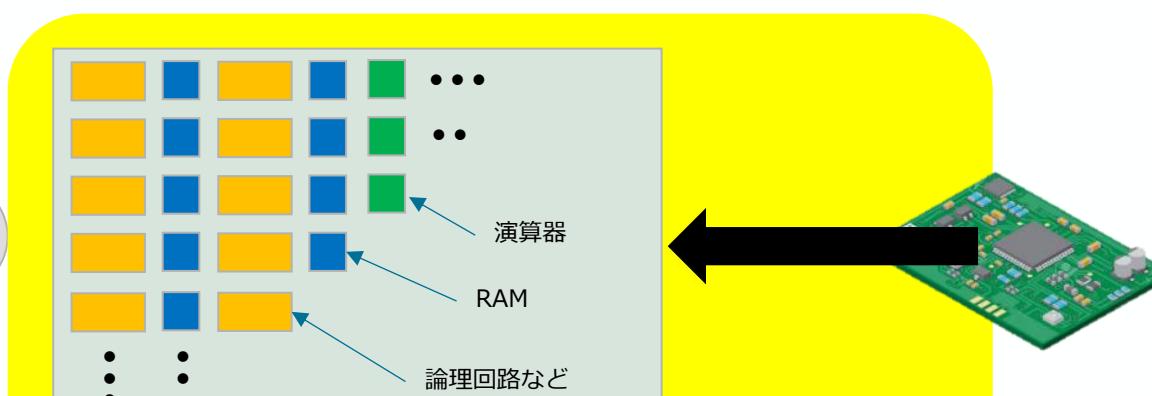

自社の生産技術エンジニアにおいては、FPGAへのプログラム修正など実施しているが**FPGAの論理設計や物理設計について理解不足**のためFPGAの機能を使い切れてない。

例:FPGA

今後、製品企画していく中で、**FPGAやAISCで何が出来るのか？どこまでの要求に応えてくれるのか？を把握出来ていない**。イノベイティブな企画が出来ない可能性がある。

# 実施イメージ：レベル感・人物像にマッチした研修・リスクリング

研修実施に至るまでの流れ

# ※NSV財団及びOpenSUSIについて

## NSV財団

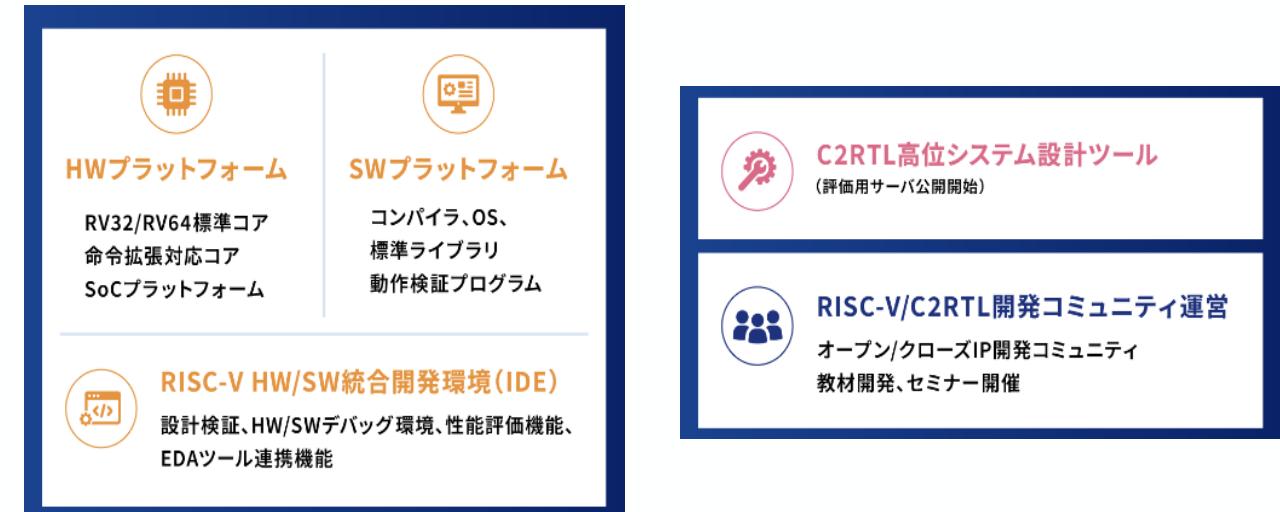

- 一般財団法人新システムビジョン研究開発機構（NSV財団：New System Vision Research and Development Institute）はロジック半導体開発力を高めるため、NEDOプロジェクトを通してRISC-Vデザインセンターを運営する。

- 同デザインセンターでは、オープン命令仕様のRISC-V(第5世代RISCプロセッサ)と全く新しい論理回路高位記述設計/検証環境である「C2RTL」を使って、最適化されたRISC-Vプロセッサを今までにない生産効率で設計/検証する手法を獲得する、学びと情報共有の場を提供している。

## OpenSUSI

- 一般社団法人OpenSUSI。国内のロングテール系のASIC開発のデマンド発掘とレガシー製造拠点との連携、設計・製造プラットフォームを構築。

- EDAで設計し、コミュニティで共有。国内の半導体アセットをオープンソースとして利用する取組。

- EDAをベースとした半導体設計人材の育成とEDAによる設計と国内レガシーファブによるASIC製造を目的としたネットワーク。